# DYNAMIC SAFETY ASSESSMENT OF FPGA-BASED SAFETY CRITICAL SYSTEMS WITH APPLICATIONS IN NUCLEAR POWER GENERATION

By:

#### **PHILLIP MCNELLES**

A THESIS SUBMITTED TO THE FACULTY OF ENERGY SYSTEMS AND NUCLEAR SCIENCE AT THE UNIVERSITY OF ONTARIO INSTITUTE OF TECHNOLOGY IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILIPSOPHY IN NUCLEAR ENGINEERING

#### © PHILLIP MCNELLES

FACULTY OF ENERGY SYSTEMS AND NUCLEAR SCIENCE

UNVIVERSITY OF ONTARIO INSTITUTE OF TECHNOLOGY

2000 SIMCOE STREET NORTH, OSHAWA, ONTARIO, CANADA, L1H 7K4

December, 2016

# DYNAMIC SAFETY ASSESSMENT OF FPGA-BASED SAFETY CRITICAL SYSTEMS WITH APPLICATIONS IN NUCLEAR POWER GENERATION

| DR. LIXUAN LU, SUPERVISOR                    |

|----------------------------------------------|

|                                              |

| DR. ANTHONY WAKER, COMMITTEE MEMBER          |

|                                              |

| MR. JOHN FROATS, COMMITTEE MEMBER            |

|                                              |

| DR. WALID MORSI IBRAHIM, UNIVERSITY EXAMINER |

|                                              |

| DR. ZHIGANG TIAN, EXTERNAL EXAMINER          |

|                                              |

| PHILLIP MCNELLES, CANDIDATE                  |

#### **Abstract**

Field Programmable Gate Arrays (FPGAS) are a type on integrated circuit that is configured by the end user to perform desired digital logic functions. FPGAs do not run any software or operating system, as the logic functions are configured as a hardware implementation on the FPGA chip. Documentation from the International Atomic Energy Agency (IAEA) states that FPGA implementations of I&C systems in Nuclear Power Plants (NPPs) is expected to increase significantly in the future. One issue facing FPGAs in the nuclear field is a lack of technical standards and design/review documentation. Therefore, the research program undertaken during this thesis considered the application of a new safety analysis methodology for the modelling and analysis of FPGA-based systems. The methodology chosen is a modern, dynamic (time-dependant) methodology known as the Dynamic Flowgraph Methodology (DFM), which is intended to be applied to digital I&C systems. Initially, a Failure Modes and Effects Analysis (FMEA) was performed to ascertain the potential failure modes that could affect FPGA-based systems, and that FMEA data was used to create and FPGA failure modes taxonomy. Using that FMEA data to provide information for fault injection, DFM was applied to analyze several FPGA-based test systems, and the results of the DFM analyses were compared and contrasted with results from Fault Tree Analysis (FTA), to determine the potential advantages and disadvantages of DFM. It was seen that DFM had several advantages when modelling clock delays, oscillating clock signals, and Multiple-Valued Logic, however for large systems DFM continues to experience the "state explosion" problem, limiting its effectiveness to small-medium sized systems. Potential avenues of future work are also presented.

#### **ACKNOWLEDGEMENT**

I would like to thank my supervisor, Dr. Lixuan Lu for taking me on as her student for PhD degree, and for all of her support and guidance throughout my degree. I am also greatly appreciative of her allowing me to intern at the Canadian Nuclear Safety Commission (CNSC) for the final two years of my doctorate, as that was another great experience.

I would also like to thank Dr. Anthony Waker and Professor John Froats for agreeing to be on my committee, as well as Dr. Walid Morsi Ibrahim and Dr. Zhigang Tian for being the examiners at my defence. All of these individuals provided me with excellent feedback and comments regarding improvements to my thesis document, and for suggestions for potential topics for the continuation of this research.

Lastly, I would like to thank Zhao Chang (Charles) Zeng and Guna Renganathan for supervising my research at the CNSC. They were always happy to help with the research projects and answer any of my questions, and I was able to learn a great deal from them. Additionally, I want to thank my directors at the CNSC, Greg Lamarre and Yolande Akl, for bringing me in to work with their divisions, as well as Sophie Gingras and Marc Leblanc, for allowing me to continue with the research program during my time in the Secretariat.

## **TABLE OF CONTENTS**

| LIST O | F FIGURES                                                                  | 10 |

|--------|----------------------------------------------------------------------------|----|

| LIST O | F TABLES                                                                   | 13 |

| GLOSS  | ARY                                                                        | 16 |

| 1 IN   | TRODUCTION                                                                 | 21 |

| 1.1 T  | hesis Outline                                                              | 21 |

| 1.2 R  | esearch Motivation                                                         | 23 |

| 1.2.1  | Motivation for FPGA Research                                               | 23 |

| 1.2.2  | Motivation for the Selection of a Dynamic Reliability Analysis Methodology | 26 |

| 1.2.3  | Motivation for the Selection of the Dynamic Flowgraph Methodology          | 28 |

| 1.3 N  | lovelty and Contribution of this Thesis                                    | 31 |

| 1.4 C  | hapter Summary                                                             | 32 |

| 2 BA   | CKGROUND                                                                   | 34 |

| 2.1 F  | PGA Background                                                             | 34 |

| 2.1.1  | FPGA Descriptions                                                          | 34 |

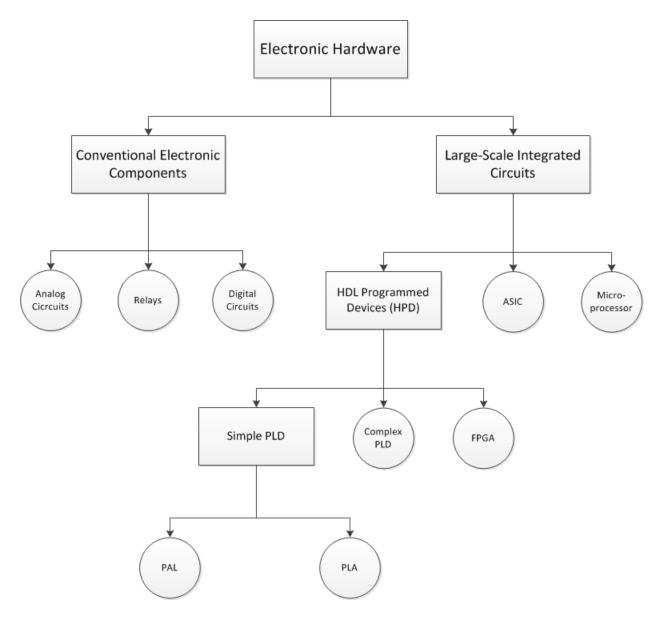

| 2.1.2  | FPGAs in the Electronic Logic Family                                       | 35 |

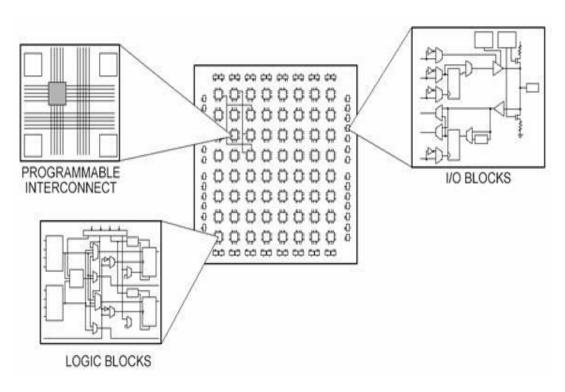

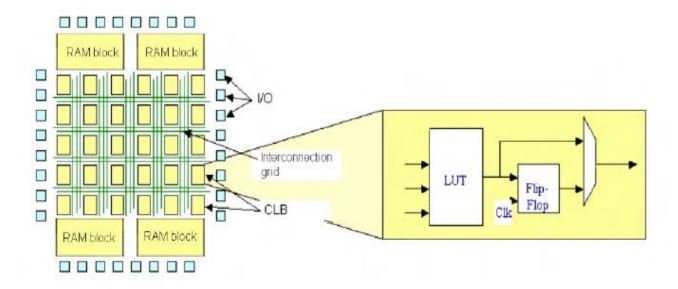

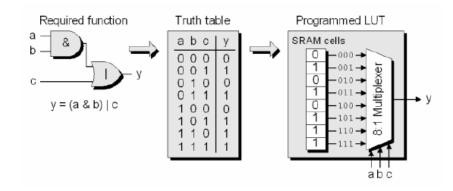

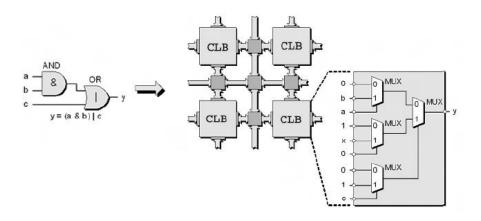

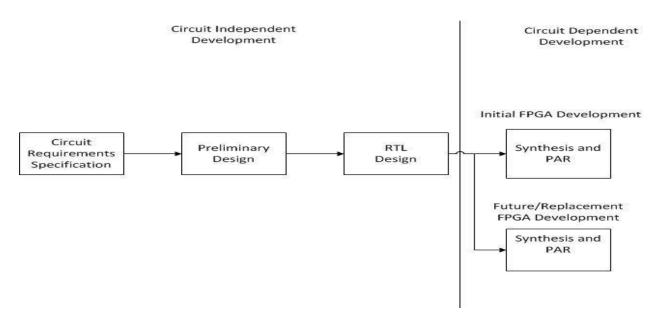

| 2.1.3  | FPGA Architecture                                                          | 39 |

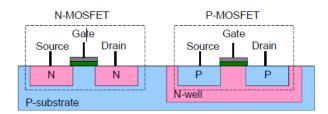

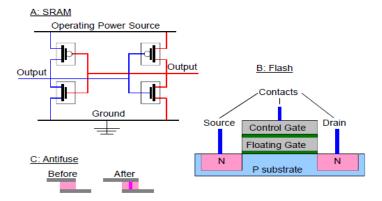

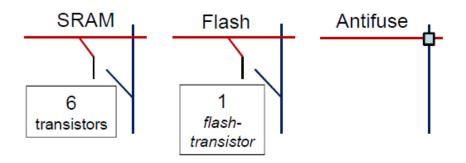

| 2.1.4  | FPGA Technologies                                                          | 43 |

| 2.1.5  | FPGA Programming                                                           | 46 |

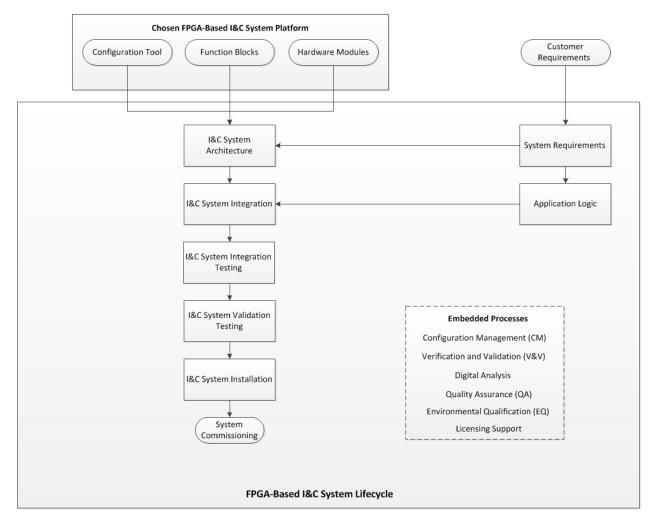

| 2.1.6  | FPGA-Based I&C System Lifecycle                                            | 56 |

| 2.1.7  | Advantages of FPGAs                                                        | 58 |

| 2.1.8  | Disadvantages of FPGAs                                                     | 61 |

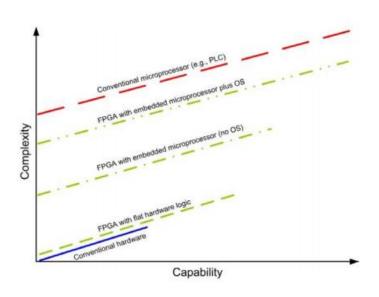

| 2.1.9  | Comparison of FPGAs and Other Electronic Control Technologies              | 63 |

| 2.1.10 | Additional Uses For FPGAs                                                  | 66 |

| 2.2 F  | PGA Literature Review                                                      | 68 |

| 2.2.1  | FPGA Developments in North America                                         | 68 |

| 2.2.2  | FPGA Developments in Asia                                                  | 78 |

| 2.2.3  | FPGA Developments in Europe                                                | 85 |

| 2.2.4  | Other FPGA Developments                                                    | 88 |

| 2.2.5  | Recent Developments                                                        | 88 |

| 2.2.6  | Research Directions Based On Literature Review                             | 89 |

| 2.3   | Reliability Analysis Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

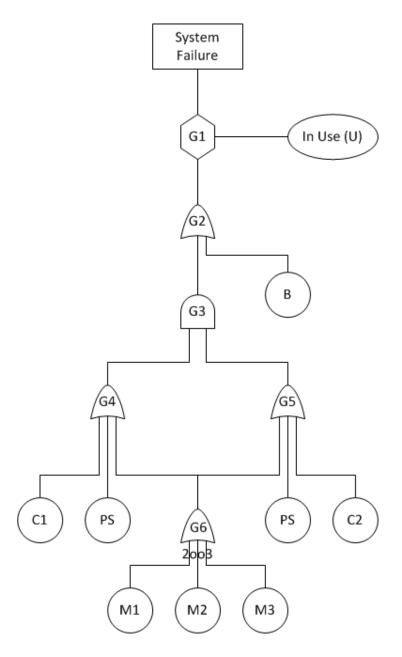

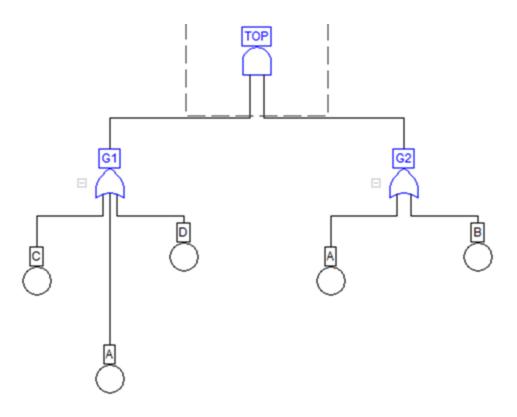

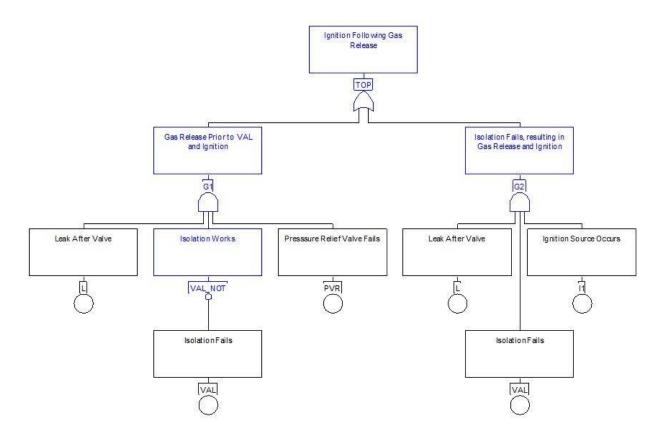

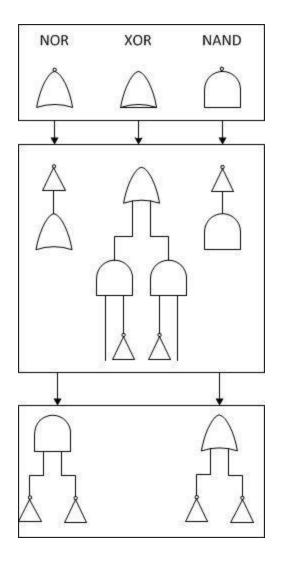

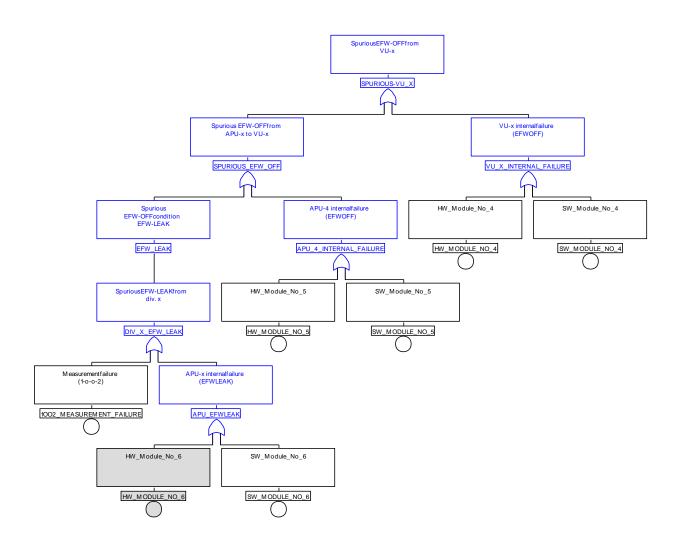

| 2.3.1 | Fault Tree Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91  |

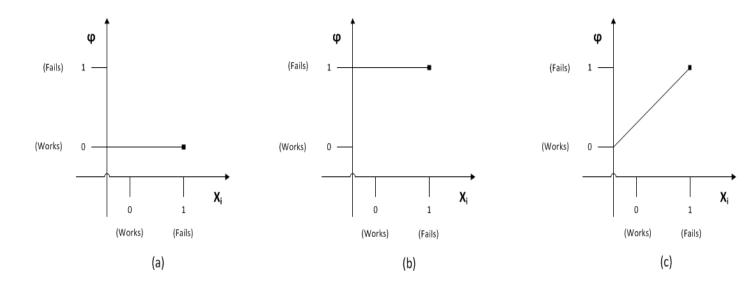

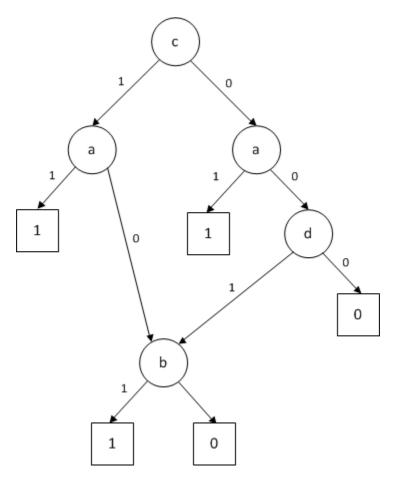

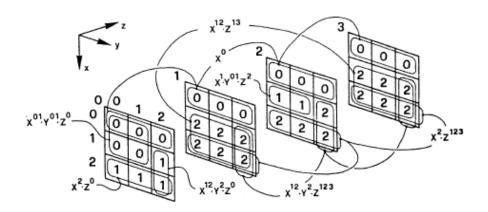

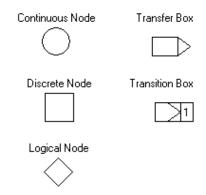

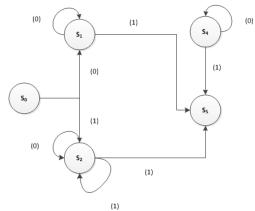

| 2.3.2 | Dynamic Flowgraph Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 121 |

| 2.4   | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 147 |

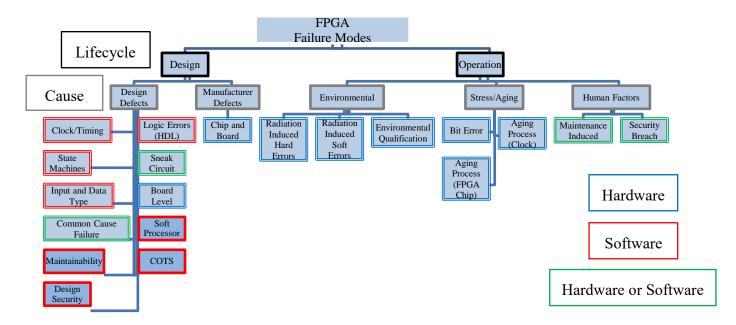

| 3. F  | PGA FAILURE MODES TAXONOMY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 148 |

| 3.1.  | FPGA Failure Modes Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 148 |

| 3.1.1 | Failure Mode and Effects Analysis (FMEA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 149 |

| 3.1.2 | Programme 1. Progr | 150 |

| 3.1.3 | S. Sets of Failure Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 152 |

| 3.1.4 | Failure Set Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 163 |

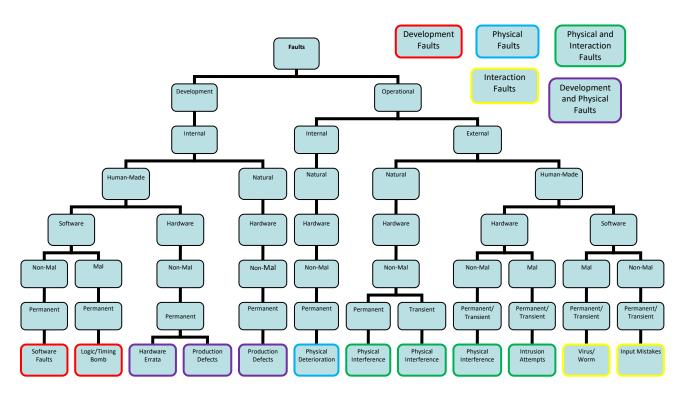

| 3.2.  | OECD-NEA Digital Failure Modes Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 165 |

| 3.2.1 | OECD-NEA Taxonomy Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 166 |

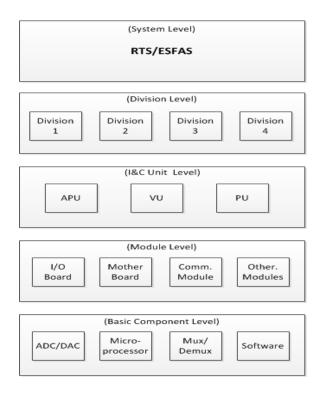

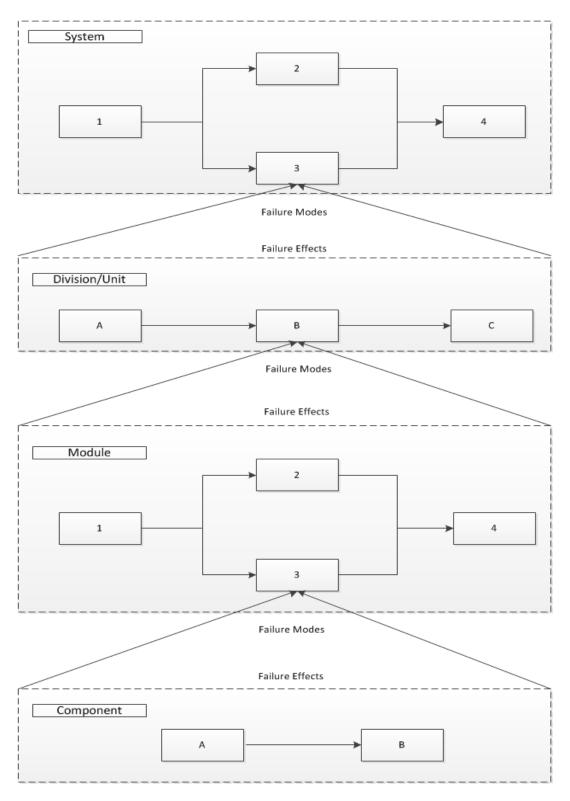

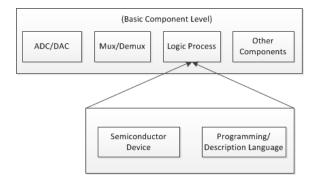

| 3.2.2 | Levels of Abstraction and Failure Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 166 |

| 3.2.3 | 8. Failure Propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 169 |

| 3.2.4 | Failure Effects Categories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 169 |

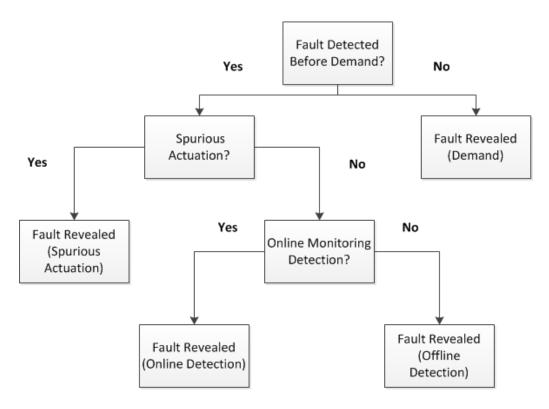

| 3.2.5 | i. Fault Uncovering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 170 |

| 3.2.6 | 6. OECD-NEA Taxonomy Basis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 171 |

| 3.2.7 | 7. OECD-NEA Categorization and the FPGA FMEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 172 |

| 3.3.  | FPGA Failure Mode Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 172 |

| 3.3.1 | Purpose of Developing the FPGA Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 172 |

| 3.3.2 | . Taxonomy Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 174 |

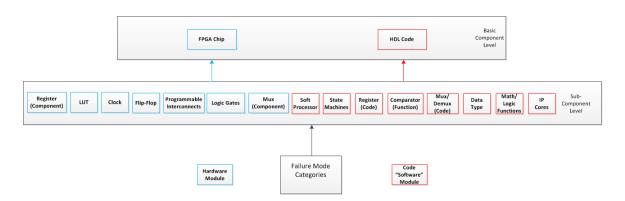

| 3.3.3 | Sub-Component Level of Abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 176 |

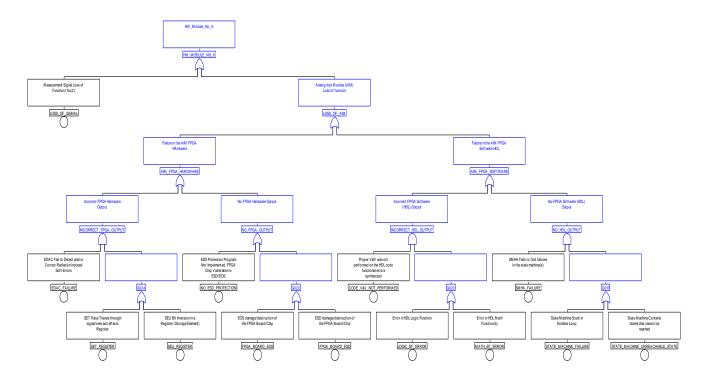

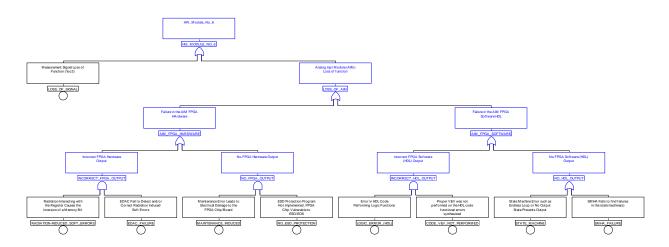

| 3.3.4 | Sub-Component Hardware Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 177 |

| 3.3.5 | Sub-Component HDL Code Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 181 |

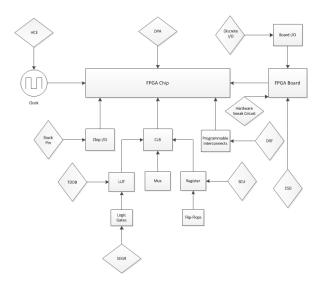

| 3.3.6 | 5. FPGA Taxonomy Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 185 |

| 3.3.7 | 7. FPGA Taxonomy PSA Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 197 |

| 3.3.8 | 2. Conclusions from the FPGA Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 200 |

| 3.4.  | Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 201 |

| 4. A  | PPLICATION OF DFM TO FPGA-BASED SYSTEM ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 202 |

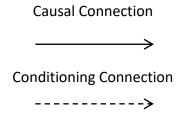

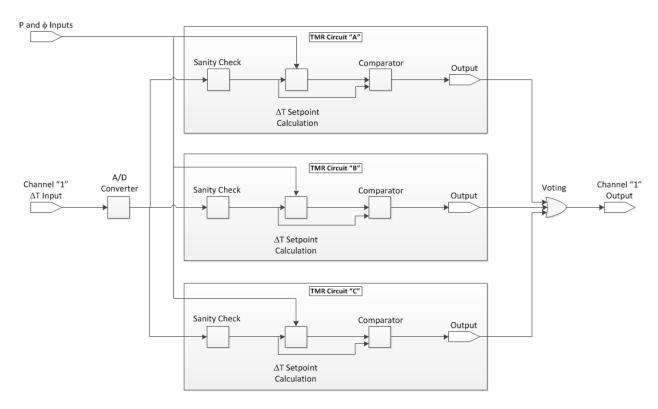

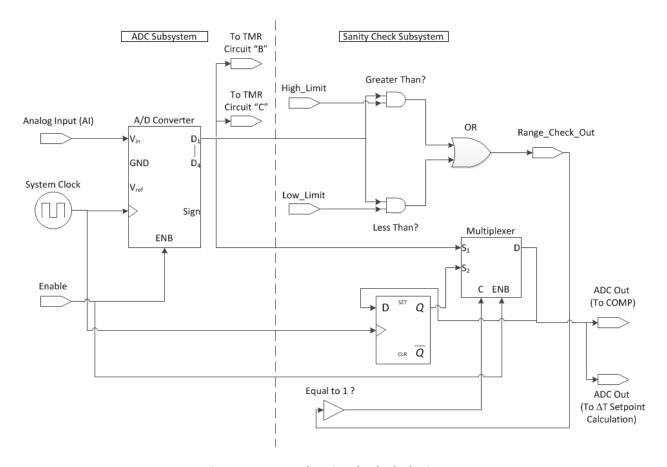

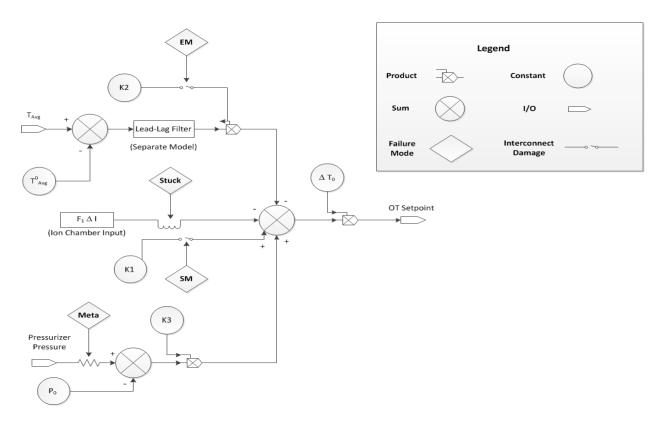

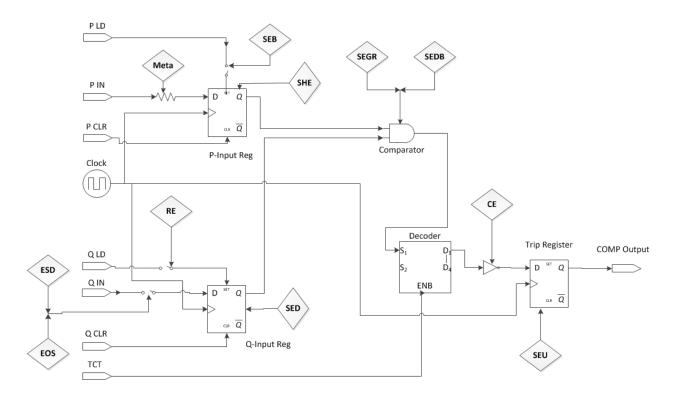

| 4.1.  | FPGA PAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 202 |

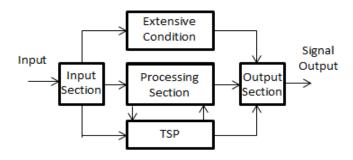

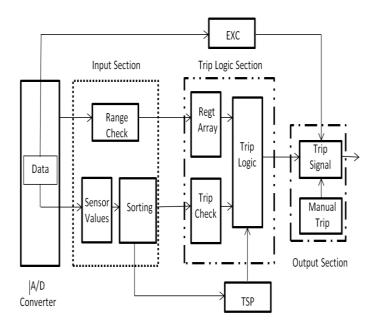

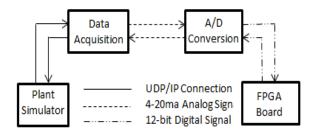

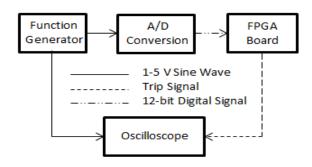

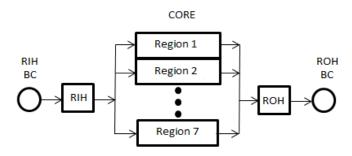

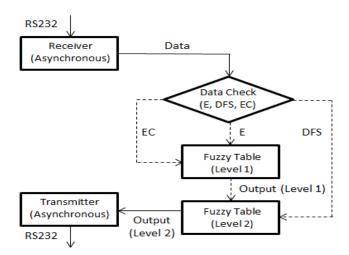

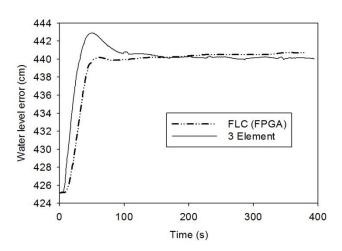

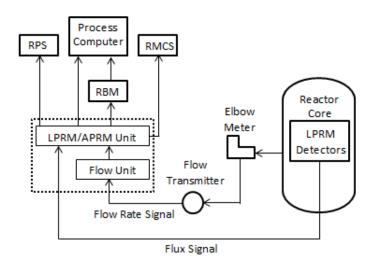

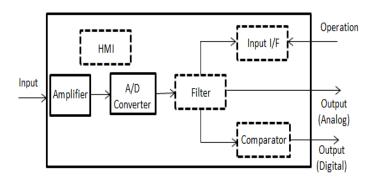

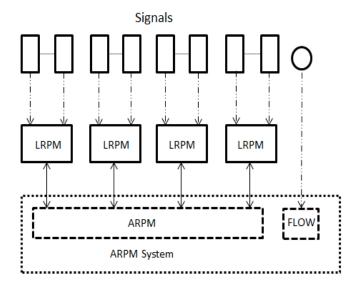

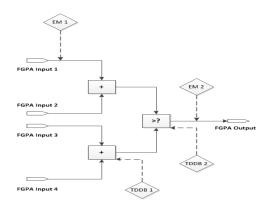

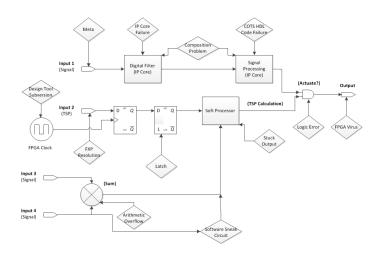

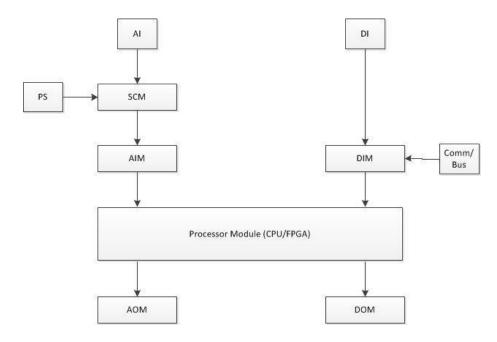

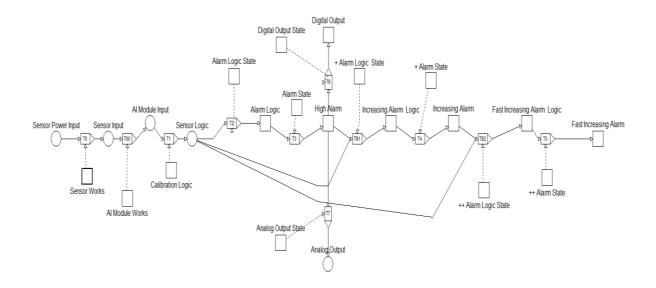

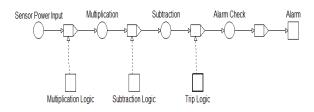

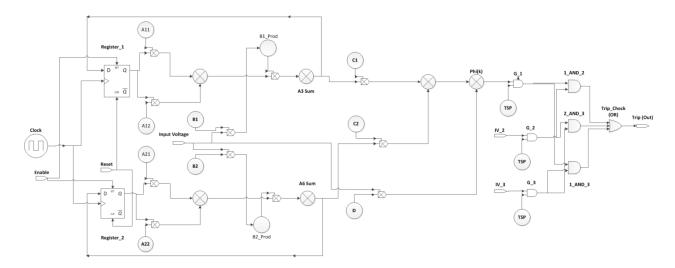

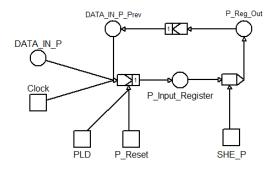

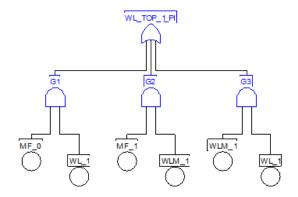

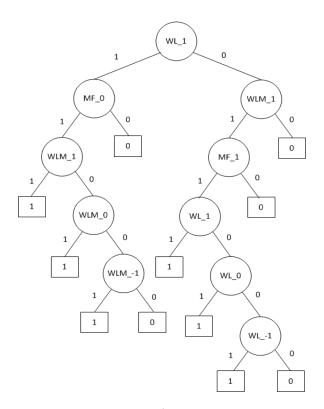

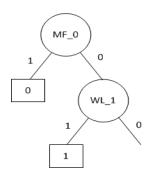

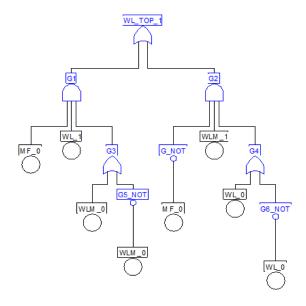

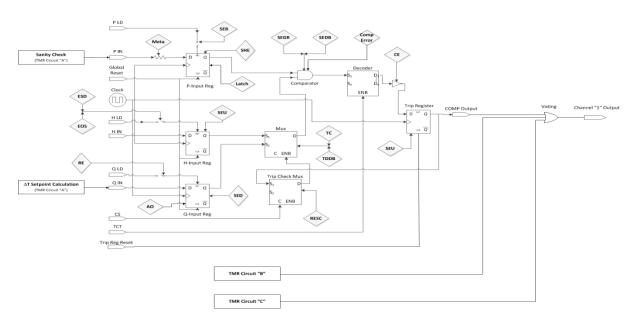

| 4.1.1 | System Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 203 |

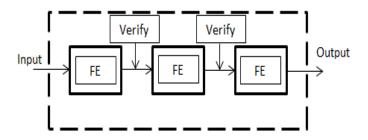

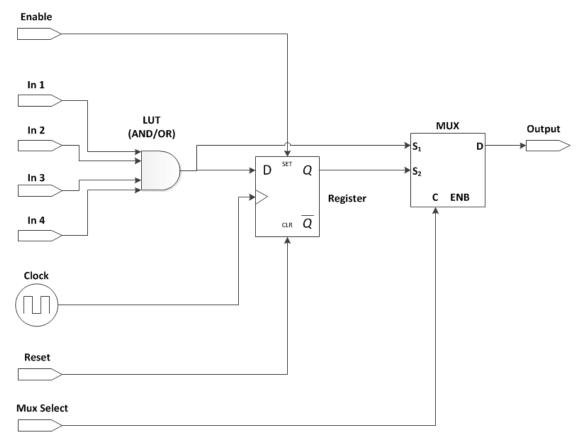

| 4.1.2 | 2. System Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 203 |

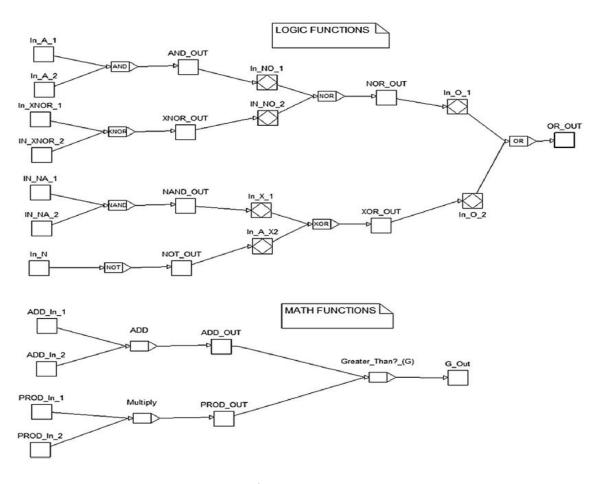

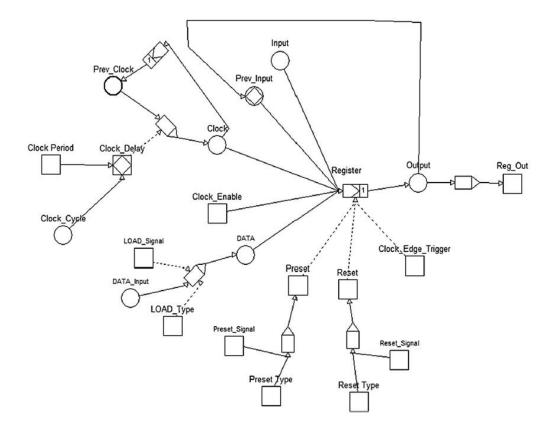

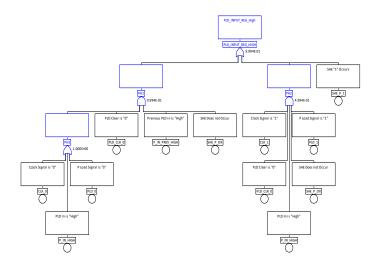

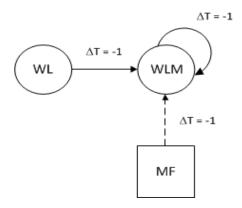

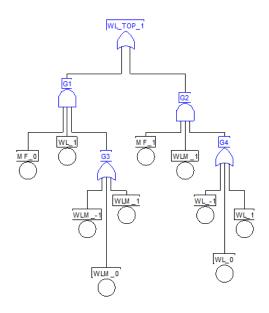

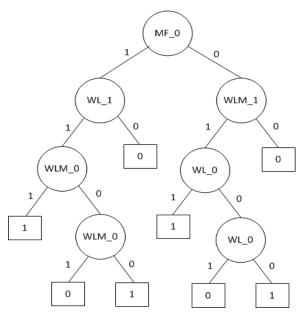

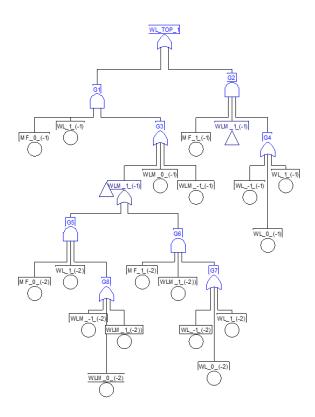

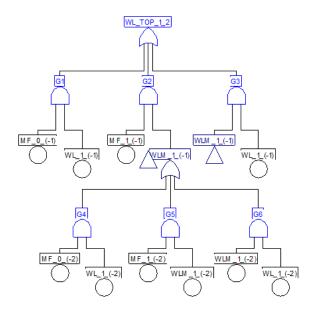

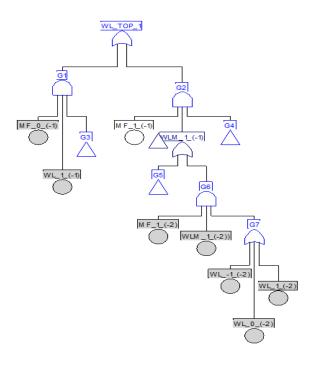

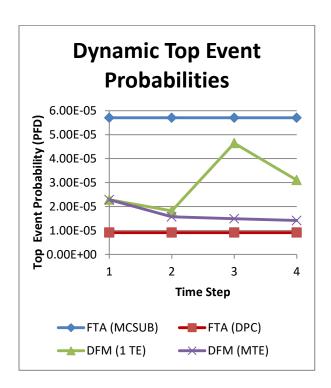

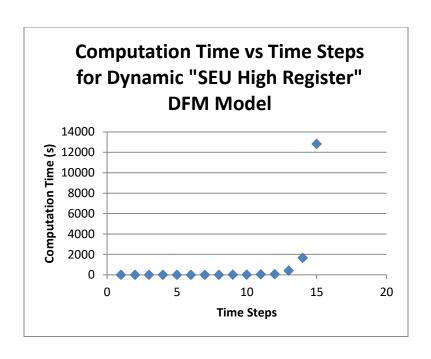

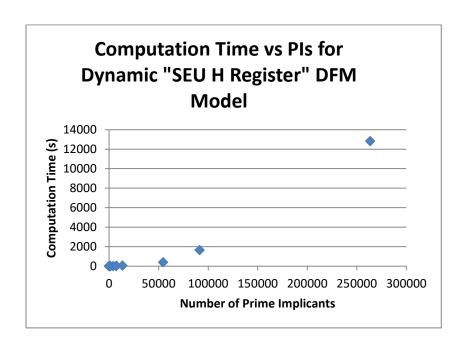

| 4.1.3 | FPGA PAMS DFM Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 205 |

| 4.1.4 | . Conclusions from FPGA PAMS DFM Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 209 |